# 5.0kV<sub>RMS</sub> Opto-Compatible Single Channel Isolated Gate Driver

### **GENERAL DESCRIPTION**

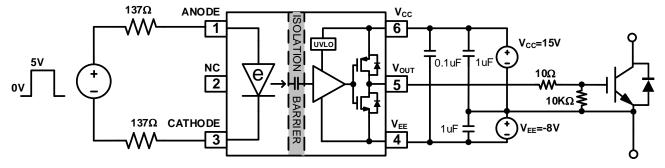

The SiLM5347AT isolated driver is an optocompatible, single channel, isolated MOSFET/IGBT gate driver with 20V UVLO voltage. The peak source current is 4A and sink current is 6A. Key features and characteristics bring significant performance and reliability upgrades over standard opto-coupler based gate drivers while maintaining pin-to-pin compatibility in both schematic and layout design. Performance highlights include high common mode transient immunity (CMTI), low propagation delay, and small pulse width distortion.

The input stage is an emulated diode which means long term reliability and excellent aging characteristics compared to traditional LEDs. It is offered in a SOP6W-T package with ≥8.0mm creepage and clearance. A mold compound from material group II which has a comparative tracking index (CTI) >400V. High performance and reliability of the SiLM5347AT makes it ideal for use in all types of motor drives, solar inverters, industrial power supplies, and appliances.

### **APPLICATION**

- AC and brushless DC motor drives

- Renewable energy inverters

- Industrial power supplies

#### **FEATURES**

- 4.0A peak source output current

- 6.0A peak sink output current

- 110ns (Max.) propagation delay

- 25ns (Max.) part-to-part delay matching

- 40ns (Max.) pulse width distortion

- 150kV/us (Min.) common mode transient immunity (CMTI)

- Gate drive supply voltage up to 40V

- 30V reverse polarity voltage handling capability on input stage

- Pin to pin compatible to opto-coupler isolated gate drivers

- SOP6W-T package with ≥8.0mm creepage and clearance

- Junction temperature, T<sub>J</sub>: -40°C to +150°C

- Safety certifications

- 5kVRMs isolation for 1 minute per UL 1577

- CQC certification per GB4943.1-2022

- DIN VDE 0884-17: 2021-10

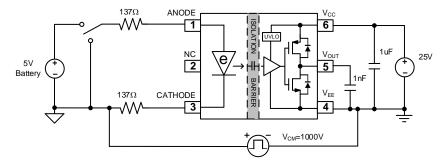

Figure 1. SiLM5347AT Typical Application

# **Table of Contents**

| General Description                        | 1  |

|--------------------------------------------|----|

| Application                                | 1  |

| Features                                   | 1  |

| PIN Configuration                          | 3  |

| PIN Description                            | 3  |

| Functional Block Diagram                   | 3  |

| Ordering Information                       | 4  |

| Absolute Maximum Ratings                   | 5  |

| Recommended Opertion Conditions            | 5  |

| ESD Ratings                                | 5  |

| Thermal Information                        | 5  |

| Package Specifications                     | 6  |

| Insulation Specifications                  | 6  |

| Safety Related Certifications              | 7  |

| Safety Limiting Values                     | 7  |

| Electrial Characteristics (DC)             | 8  |

| Switching Characteristics (AC)             | 9  |

| Parameter Measurement Information          | 10 |

| Propagation Delay, Rise Time and Fall Time | 10 |

| IOH and IOL Testing                        | 10 |

| CMTI Testing                               | 10 |

| Feature Description                        | 11 |

| Input Stage                                | 11 |

| Under Voltage Lockout (UVLO)               | 12 |

| Typical Input Configuration Circuit        | 12 |

| Layout                                     | 12 |

| Package Case Outlines                      | 13 |

| Reflow Profile Guidance                    | 14 |

| Revision History                           | 15 |

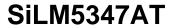

## **PIN CONFIGURATION**

| Package | Pin Configuration (Top View)                                          |

|---------|-----------------------------------------------------------------------|

| SOP6W-T | ANODE 1 0 6 V <sub>CC</sub> NC 2 5 V <sub>OUT</sub> 4 V <sub>EE</sub> |

### **PIN DESCRIPTION**

| No. | Pin             | Description                |

|-----|-----------------|----------------------------|

| 1   | ANODE           | Anode                      |

| 2   | NC              | No Connection              |

| 3   | CATHODE         | Cathode                    |

| 4   | V <sub>EE</sub> | Negative Power Supply Rail |

| 5   | Vouт            | Gate Drive Output          |

| 6   | Vcc             | Positive Power Supply Rail |

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. SiLM5347AT Functional Block Diagram

# **ORDERING INFORMATION**

| Order Part No.  | Package          | QTY       |

|-----------------|------------------|-----------|

| SiLM5347ATCR-DG | SOP6W-T, Pb-Free | 1000/Reel |

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol              | ymbol Definition                          |     | Max | Unit |

|---------------------|-------------------------------------------|-----|-----|------|

| I <sub>F(AVG)</sub> | Average Input Current                     |     | 25  | mA   |

| V <sub>R</sub>      | V <sub>R</sub> Reverse Input Voltage      |     | 30  | V    |

| Vcc -Vee            | Output supply voltage                     |     | 45  | V    |

| ΤJ                  | T <sub>J</sub> Junction temperature -40 1 |     | 150 | °C   |

| Ts                  | Storage temperature                       | -55 | 150 |      |

## **RECOMMENDED OPERTION CONDITIONS**

| Symbol                           | Definition                                          | Min  | Max | Unit |

|----------------------------------|-----------------------------------------------------|------|-----|------|

| V <sub>CC</sub> -V <sub>EE</sub> | Output Supply Voltage                               | 21.5 | 40  | V    |

| I <sub>F</sub> (ON)              | ON) Input Diode Forward Current (Diode "ON")        |      | 16  | mA   |

| V <sub>F</sub> (OFF)             | (OFF) Anode Voltage - Cathode Voltage (Diode "OFF") |      | 0.9 | V    |

| TJ                               | Junction temperature                                |      | 150 | °C   |

| T <sub>A</sub>                   | Ambient temperature                                 | -40  | 125 | °C   |

# **ESD RATINGS**

| Symbol           | Definition | Value | Unit |

|------------------|------------|-------|------|

| V <sub>ESD</sub> | НВМ        | ±4000 | V    |

| VESD             | CDM        | ±2000 | v    |

## THERMAL INFORMATION

| Symbol Definition |                                                               | Value | Unit |

|-------------------|---------------------------------------------------------------|-------|------|

| R <sub>θJA</sub>  | Junction to ambient thermal resistance                        | 125   | °C/W |

| R <sub>θ</sub> JC | R <sub>θJC</sub> Junction to case (top) thermal resistance 66 |       | °C/W |

| Ψлτ               | Junction to top characterization parameter                    | 30    | °C/W |

# **PACKAGE SPECIFICATIONS**

| Symbol | Definition                              | Min | Тур              | Max | Units |

|--------|-----------------------------------------|-----|------------------|-----|-------|

| Rıo    | Resistance (Input Side to Output Side)  |     | 10 <sup>12</sup> |     | Ω     |

| Сю     | Capacitance (Input Side to Output Side) |     | 0.8              |     | pF    |

| CIN    | Input Capacitance                       |     | 30               |     | pF    |

# **INSULATION SPECIFICATIONS**

| Symbol                | Definition                                | Test Condition                                                                                                                     | Value     | Units            |

|-----------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|

| CLR                   | External clearance                        | Shortest terminal to terminal distance through air                                                                                 | ≥8        | mm               |

| CPG                   | External creepage                         | Shortest terminal to terminal distance across the package surface                                                                  | ≥8        | mm               |

| DTI                   | Distance through the insulation           | Minimum internal gap                                                                                                               | >16       | um               |

| СТІ                   | Comparative tracking index                | DIN EN 60112 (VDE 0303-11),<br>IEC 60112                                                                                           | >400      | V                |

|                       | Material Group                            |                                                                                                                                    | II        |                  |

|                       |                                           | Rated mains voltages ≤150Vrms                                                                                                      | IV        |                  |

|                       |                                           | Rated mains voltages ≤300Vrms                                                                                                      | IV        |                  |

|                       | Overvoltage category                      | Rated mains voltages ≤600Vrms                                                                                                      | III       |                  |

|                       |                                           | Rated mains voltages<br>≤1000Vrms                                                                                                  | II        |                  |

| DIN V VD              | E 0884-11 <sup>(1)</sup>                  |                                                                                                                                    |           | 1                |

| Viorm                 | Maximum repetitive peak isolation voltage |                                                                                                                                    | 1414      | V <sub>PK</sub>  |

| V <sub>IOWM</sub>     | Maximum isolation working voltage         |                                                                                                                                    | 1000      | V <sub>RMS</sub> |

| V <sub>ІОТМ</sub>     | Maximum transient isolation voltage       | 60s                                                                                                                                | 7000      | V <sub>PK</sub>  |

| V <sub>IOSM</sub>     | Maximum surge isolation voltage           | Test method per IEC62368,<br>1.2/50us waveform, V <sub>TEST</sub> =1.6 x<br>V <sub>IOSM</sub>                                      | 6250      | V <sub>PK</sub>  |

| q <sub>pd</sub>       | Apparent charge                           | Method b2: $V_{pd(m)}$ =1.875 x $V_{IORM}$ , $tm$ =1 s                                                                             | ≤5        | pC               |

|                       | Climatic Category                         |                                                                                                                                    | 40/125/21 |                  |

|                       | Pollution Degree                          |                                                                                                                                    | 2         |                  |

| UL1577 <sup>(1)</sup> | .1                                        |                                                                                                                                    |           | 1                |

| Viso                  | Withstand Isolation Voltage               | V <sub>TEST</sub> =V <sub>ISO</sub> , t=60s (qualification),<br>V <sub>TEST</sub> =1.2 x V <sub>ISO</sub> , t=1s (100% production) | 5000      | V <sub>RMS</sub> |

<sup>1.</sup>Certification pending

# **SAFETY RELATED CERTIFICATIONS**

| VDE                                      | UL                                       | CQC                                                                                 |

|------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------|

| DIN VDE 0884-17: 2021-10                 | UL 1577 component recognition            | Certified according to                                                              |

|                                          | program                                  | GB4943.1-2022                                                                       |

| Reinforced Insulation                    | Single protection, 5000 V <sub>RMS</sub> | Reinforced insulation,                                                              |

| V <sub>IORM</sub> = 1414 V <sub>PK</sub> | Altitude ≤ 5000m, Tropical clin          | Altitude ≤ 5000m, Tropical climate,<br>400 V <sub>RMS</sub> maximum working voltage |

| VIOTM = 7000 VPK                         |                                          | 400 VRMS Maximum Working Voltage                                                    |

| VIOSM = 6250 VPK                         |                                          |                                                                                     |

| Pending                                  | Pending                                  | Pending                                                                             |

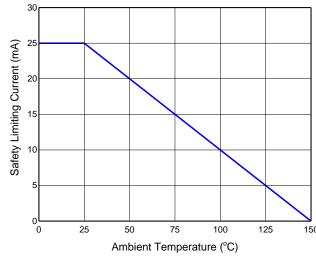

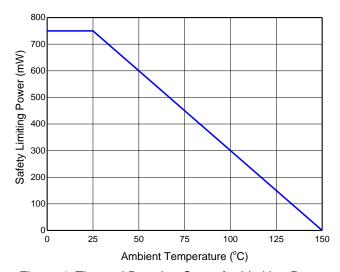

### **SAFETY LIMITING VALUES**

| Symbol | Parameter                               | Condition                                                                          | Value | Unit |

|--------|-----------------------------------------|------------------------------------------------------------------------------------|-------|------|

| Is     | Safety input, output, or supply current | $R_{\theta JA}$ =125°C/W, $V_{CC}$ - $V_{EE}$ = 30V, $T_{J}$ =150°C, $T_{A}$ =25°C | 25    | mA   |

| Ps     | Safety input, output, or total power    | R <sub>θ</sub> JA=125°C/W, T <sub>J</sub> =150°C, T <sub>A</sub> =25°C             | 750   | mW   |

| Ts     | Maximum safety temperature              |                                                                                    | 150   | °C   |

Figure 3. Thermal Derating Curve for Limiting Current per VDE

Figure 4. Thermal Derating Curve for Limiting Power per VDE

# **ELECTRIAL CHARACTERISTICS (DC)**

$V_{CC}$ - $V_{EE}$  = 25V,  $V_{EE}$  = GND and  $T_A$  = 25°C unless otherwise specified. All min and max specifications are at  $T_A$  = -40°C to 125°C

| Symbol              | Parameter                                   | Condition                                                                                        | Min  | Тур  | Max  | Unit     |

|---------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------|------|------|------|----------|

| INPUT               | 1                                           | L                                                                                                |      |      |      | l        |

| I <sub>FLH</sub>    | Input Forward Threshold Current Low to High |                                                                                                  | 1.6  | 2.1  | 3    | mA       |

| V <sub>F</sub>      | Input Forward Voltage                       | I <sub>F</sub> =10mA                                                                             | 2.1  | 2.25 | 2.5  | V        |

| ΔV <sub>F</sub> /ΔΤ | Temp Coefficient of Input Forward Voltage   | I <sub>F</sub> =10mA                                                                             |      | 0.5  |      | mV/°C    |

| $V_{R}$             | Input Reverse Breakdown Voltage             | I <sub>R</sub> =10uA                                                                             | 30   |      |      | V        |

| OUTPUT              |                                             |                                                                                                  |      |      | I    | <u> </u> |

| Іон                 | High Level Peak Output Current              | $V_{CC}$ =25V,I <sub>F</sub> =10mA, $C_{VDD}$ =10uF, $C_{LOAD}$ =220nF                           |      | 4.0  |      | А        |

| loL                 | Low Level Peak Output Current               | V <sub>CC</sub> =25V, V <sub>F</sub> =0V,<br>C <sub>VDD</sub> =10uF,<br>C <sub>LOAD</sub> =220nF |      | 6.0  |      | А        |

| V <sub>OH</sub>     | High Level Output Voltage                   | I <sub>F</sub> =10mA, I <sub>O</sub> =-20mA<br>"With respect to Vcc"                             |      | 26   |      | mV       |

| V <sub>OL</sub>     | Low Level Output Voltage                    | V <sub>F</sub> =0V, I <sub>O</sub> =20mA                                                         |      | 13   |      | mV       |

| UNDER VO            | OLTAGE LOCKOUT                              | ı                                                                                                | I    | 1    | I    | l        |

| UVLO <sub>R</sub>   | Under Voltage Lockout Vcc rising            | I <sub>F</sub> =10mA                                                                             | 18.5 | 20   | 21.5 | V        |

| UVLO <sub>F</sub>   | Under Voltage Lockout Vcc falling           | I <sub>F</sub> =10mA                                                                             | 17   | 18.5 | 20   | V        |

| UVLO <sub>HYS</sub> | Under Voltage Lockout Hysteresis            |                                                                                                  |      | 1.5  |      | V        |

# **SWITCHING CHARACTERISTICS (AC)**

$V_{CC}$ - $V_{EE}$  = 25V,  $V_{EE}$  = GND and  $T_A$  = 25°C unless otherwise specified. All min and max specifications are at  $T_A$  = -40°C to 125°C

| Symbol            | Parameter                                             | Condition                                                                                   | Min | Тур | Max | Unit  |

|-------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| t <sub>PLH</sub>  | Propagation delay, Low to High                        |                                                                                             |     | 75  | 110 | ns    |

| tpHL              | Propagation delay, High to Low                        | C <sub>LOAD</sub> =1nF, f <sub>sw</sub> =20kHz,                                             |     | 75  | 110 | ns    |

| tr                | Turn on rise time                                     | (50% Duty Cycle),                                                                           |     |     | 25  | ns    |

| t <sub>f</sub>    | Turn off fall time                                    | 7 700 201                                                                                   |     |     | 15  | ns    |

| t <sub>PWD</sub>  | Pulse Width Distortion                                |                                                                                             |     |     | 40  | ns    |

| t <sub>PDD</sub>  | Propagation Delay Difference<br>Between Any Two Parts |                                                                                             |     |     | 25  | ns    |

| tuvlo_rec         | UVLO Recovery Delay                                   | Vcc Rising from 0V to 25V                                                                   |     | 22  | 30  | us    |

| CMTI <sub>H</sub> | Output High Level Common Mode<br>Transient Immunity   | I <sub>F</sub> =10mA, V <sub>CM</sub> =1000V,<br>V <sub>CC</sub> =25V, T <sub>A</sub> =25°C | 150 | 200 |     | kV/us |

| CMTI∟             | Output Low Level Common Mode<br>Transient Immunity    | V <sub>F</sub> =0V, V <sub>CM</sub> =1000V,<br>V <sub>CC</sub> =25V, T <sub>A</sub> =25°C   | 150 | 200 |     | kV/us |

### PARAMETER MEASUREMENT INFORMATION

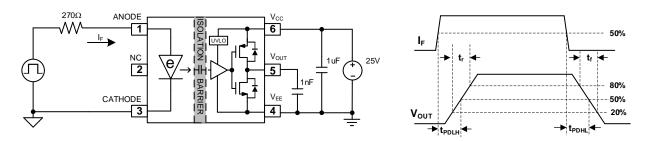

### Propagation Delay, Rise Time and Fall Time

Figure 5 shows the propagation delay from the input forward current  $I_F$ , to  $V_{OUT}$ . This figure also shows the circuit used to measure the rise  $(t_r)$  and fall $(t_f)$  times and the propagation delays  $t_{PDLH}$  and  $t_{PDHL}$ .

Figure 5. Propagation Delay, Rise Time and Fall Time

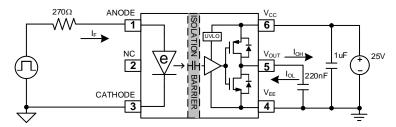

### **IOH and IOL Testing**

Figure 6 shows the circuit used to measure the output drive current  $I_{OL}$  and  $I_{OH}$ . A load capacitance of 220nF is used at the output. The peak dv/dt of the capacitor voltage is measured in order to determine the peak source and sink currents of the gate driver.

Figure 6. IoH and IoL

### **CMTI Testing**

Figure 7 is the simplified diagram of the CMTI testing. Common mode voltage is set to 1000V. The test is performed with  $I_F=10mA$  ( $V_{OUT}=High$ ) and  $V_F=0V$  ( $V_{OUT}=Low$ ).

Figure 7. CMTI Test Circuit

### FEATURE DESCRIPTION

SiLM5347AT is a single channel isolated gate driver, with an opto-compatible input stage, that can drive IGBTs and MOSFETs. It has 4.0A peak output current capability with maxim output driver supply voltage of 40V. The inputs and the outputs are galvanically isolated. SiLM5347AT is offered in SOP6W-T package with >8.5mm creepage and clearance. The reinforced isolation rating is 5kV<sub>RMS</sub> for 60 seconds. It is pin-to-pin compatible with standard opto-coupler isolated gate drivers. While standard opto-coupler isolated gate drivers use an LED as the input stage, SiLM5347AT uses an emulated diode as the input stage which does not use light emission to transmit signals across the isolation barrier. The input stage is isolated from the driver stage by dual, series HV SiO2 capacitors in full differential configuration that not only provides reinforced isolation but also offers great performance of common mode transient immunity >150kV/us. The e-diode input stage along with capacitive isolation technology gives SiLM5347AT several performance advantages over standard opto-coupler isolated gate drivers.

- Since the emulated diode does not use light emission for its operation, the reliability and aging characteristics of SiLM5347AT are naturally superior to those of standard opto-coupler isolated gate drivers.

- Higher ambient operating temperature range of 125°C, compared to only 105°C for most opto-coupler isolated gate drivers

- The e-diode forward voltage drop has less part-to-part variation and smaller variation across temperature.

Hence, the operating point of the input stage is more stable and predictable across different parts and operating temperature

- Higher common mode transient immunity than opto-coupler isolated gate drivers

- Smaller propagation delay than opto-coupler isolated gate drivers

- Due to superior process controls achievable in capacitive isolation compared to opto-coupler isolation, there is less part-to-part skew in the propagation delay, making the system design simpler and more robust

- Smaller pulse width distortion than opto-coupler isolated gate drivers

### **Input Stage**

The input stage of SiLM5347AT is an emulated diode. When the emulated diode is forward biased by applying a positive voltage to the Anode with respect to the Cathode, a forward current,  $I_F$ , flows into the e-diode. The forward voltage drop across the e-diode is 2.25V (typ). An external resistor should be used to limit the forward current. The recommended range for the forward current is 7mA to 16mA. When  $I_F$  exceeds the input forward threshold current  $I_{FLH}$  (2.1mA typ), the  $V_{OUT}$  is driver high. If the  $I_F$  is lower than  $I_{FLH}$ , or the voltage between Anode and Cathode is reverse biased, the  $V_{OUT}$  is driven low.

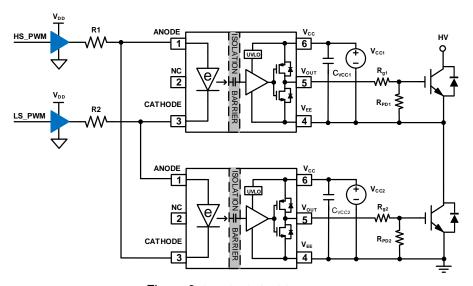

The reverse breakdown voltage of the e-diode is up to 30V. The large reverse breakdown voltage of the e-diode enables SiLM5347AT to be operated in interlock architecture as shown in Figure 8. The example shows two gate drivers driving a set of IGBTs. The inputs of the gate drivers are connected as shown in Figure 8 and driven by two buffers that are controlled by the MCU. Interlock architecture prevents both the e-diodes from being "ON" at the same time, preventing shoot through in the IGBTs. It also ensures that if both PWM signals are erroneously stuck high (or low) simultaneously, both gate driver outputs will be driven low.

Figure 8. Interlock Architecture

### Under Voltage Lockout (UVLO)

The SiLM5347AT integrates the UVLO protection on the  $V_{CC}$  to prevent an under driven condition on IGBTs and MOSFETs. When  $V_{CC}$  is lower than UVLO<sub>R</sub> during start up or lower than UVLO<sub>F</sub> after start up, the UVLO feature holds the  $V_{OUT}$  low, regardless of the input forward current. A hysteresis on the UVLO feature prevents glitch when there is noise from the power supply. When  $V_{CC}$  drops below UVLO<sub>F</sub>, a recovery delay ( $t_{UVLO\_REC}$ ) occurs on the output when the supply voltage rises above UVLO<sub>R</sub> again.

### **Typical Input Configuration Circuit**

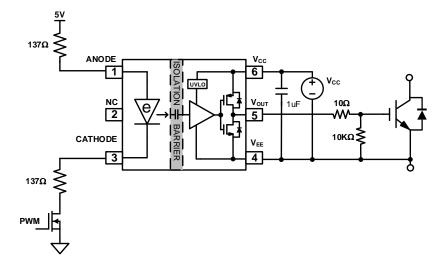

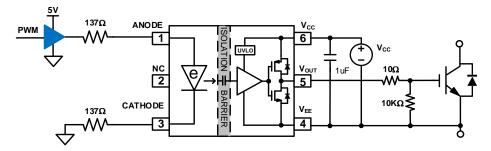

The circuit in Figure 9 and Figure 10 show two typical input configuration circuits for SiLM5347AT to driver IGBT.

Figure 9. Single MOSFET Circuit as Input Drive of SiLM5347AT to Drive IGBT

Figure 10. Buffer Circuit as Input Drive of SiLM5347AT to Drive IGBT

### Layout

In order to achieve optimum performance for the SiLM5347AT, some suggestions on PCB layout.

### Component placement:

- Low ESR and low ESL capacitors must be connected close to the device between the V<sub>CC</sub> and V<sub>EE</sub> pins to bypass noise and to support high peak currents when turning on the external power transistor.

- To avoid large negative transients on the VEE pins connected to the switch node, the parasitic inductances between the source of the top transistor and the source of the bottom transistor must be minimized.

### Grounding considerations:

Limiting the high peak currents that charge and discharge the transistor gates to a minimal physical area is

essential. This limitation decreases the loop inductance and minimizes noise on the gate terminals of the

transistors. The gate driver must be placed as close as possible to the transistors.

### High-voltage considerations:

To ensure isolation performance between the primary and secondary side, avoid placing any PCB traces or copper below the driver device. A PCB cutout or groove is recommended in order to prevent contamination that may compromise the isolation performance.

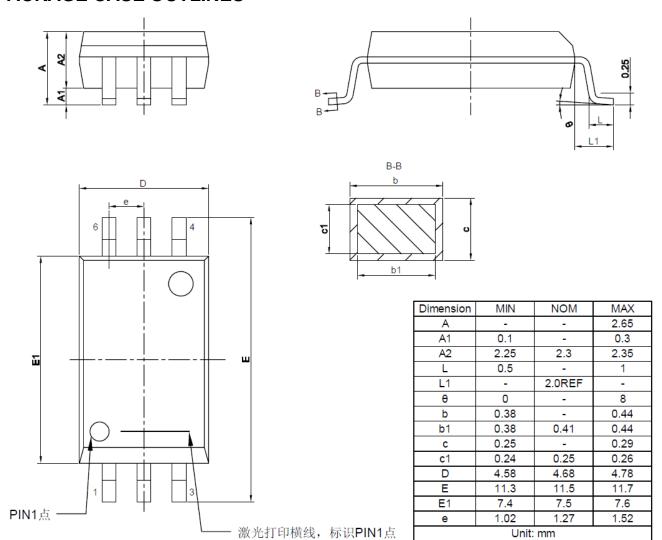

# **PACKAGE CASE OUTLINES**

Figure 11. SOP6W-T Package Outline Dimensions

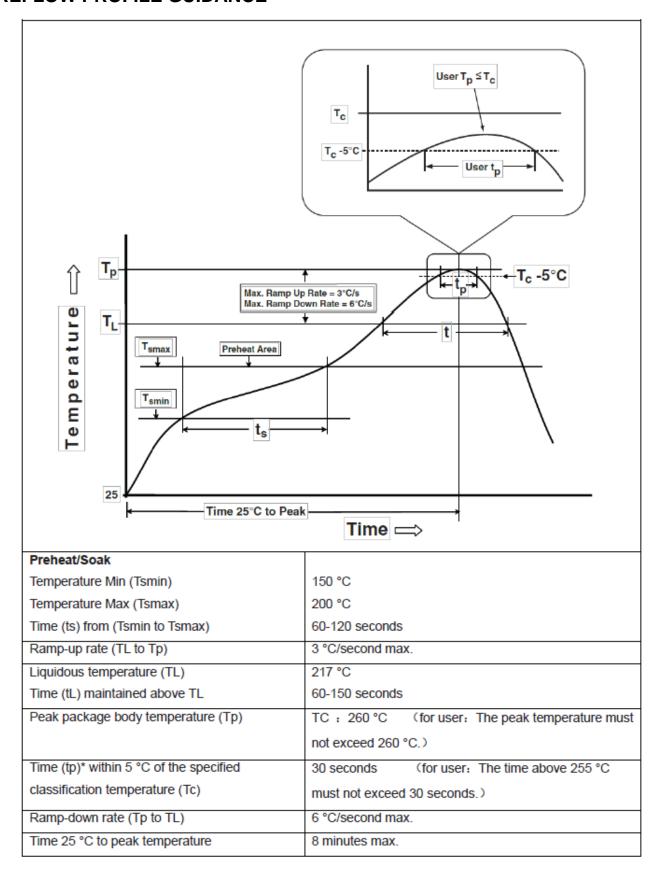

### **REFLOW PROFILE GUIDANCE**

## **REVISION HISTORY**

Note: page numbers for previous revisions may differ from page numbers in current version

| Page or Item                  | Subjects (major changes since previous revision) |  |  |  |

|-------------------------------|--------------------------------------------------|--|--|--|

| Rev 1.0 datasheet: 2023-11-29 |                                                  |  |  |  |

| Whole document                | Initial datasheet release                        |  |  |  |