SILLUMIN

# 30V, 5A Dual-Channel Low-Side Gate Driver

#### **GENERAL DESCRIPTION**

The SiLM27624 is a dual-channel, high-speed, lowside gate drivers that can effectively drive MOSFET and IGBT power switches. Using a design that inherently minimizes shoot-through current, SiLM27624 can source and sink high peak-current pulses into capacitive loads offering rail-to-rail drive capability and extremely small propagation delay, typically 20ns.

The SiLM27624 provides 5.0 A source, 5.0 A sink peak-drive current capability at 12V VDD supply.

#### APPLICATIONS

- Switching mode power supplies

- DC-to-DC converters

- Motor Control, solar power

- Gate drive for emerging wide band-gap power devices such as GaN

#### FEATURES

- Two independent gate drive channels

- 5.0 A peak source and 5.0 A peak sink current drive capability

- Fast propagation delay (20ns typical)

- Fast rise and fall time (7ns and 6ns typical)

- 4.5 to 30V single supply range

- Under-voltage lockout

- TTL and CMOS compatible input logic threshold

- Ability to handle negative voltages (-5V) at inputs

- 2ns delay matching between two channels

- Two outputs are paralleled for higher drive current

- Outputs held in low when inputs floating

- Operating temperature range of -40°C to 150°C

- SOP8 and MSOP8-EP package options

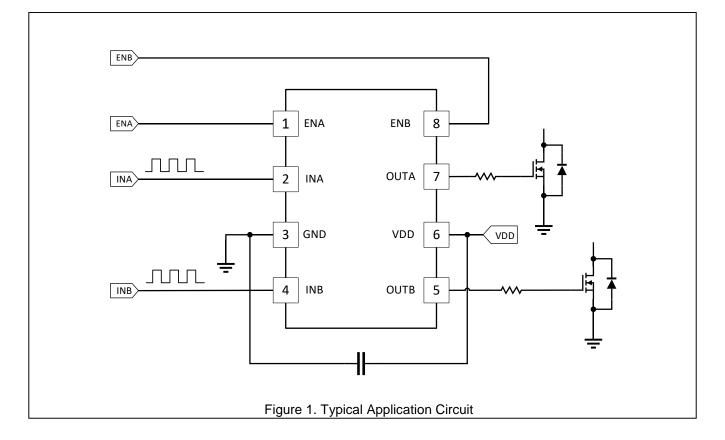

### **TYPICAL APPLICATION CIRCUIT**

# SILUMIN

## **Table of Contents**

| General Description1                      |

|-------------------------------------------|

| Applications1                             |

| Features1                                 |

| Typical Application Circuit1              |

| PIN Configuration                         |

| PIN Description                           |

| Functional Block Diagram4                 |

| Absolute Maximum RatingS <sup>1,2,3</sup> |

| Recommended Operation Conditions          |

| Ordering Information                      |

| Dynamic Electrical Characteristics        |

| Static Electrical Characteristics         |

| Feature Description8                      |

| VDD and Under-Voltage Lockout8            |

| Input Stage8                              |

| Enable Function                           |

| Output Stage8                             |

| Package Case Outlines9                    |

| Revision History                          |

## **PIN CONFIGURATION**

| Package  | Pin Configuration (Top View) |        |

|----------|------------------------------|--------|

| SOP8     |                              |        |

|          |                              |        |

|          | ENA 1                        | 8 ENB  |

|          | INA 2                        | 7 OUTA |

|          | GND 3                        | 6 VDD  |

|          | INB 4                        | 5 OUTB |

|          |                              |        |

| MSOP8-EP |                              |        |

|          |                              |        |

|          | ENA 1                        | 8 ENB  |

|          | INA 2<br>Exposed Pad         | 7 OUTA |

|          | GND 3                        | 6 VDD  |

|          | INB 4                        | 5 OUTB |

|          |                              |        |

## **PIN DESCRIPTION**

| No. | Pin  | Description                                                                                                                                                                                                                                                                                 |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ENA  | Enable input for channel A. When ENA is low, the channel A output is disabled regardless of the INA state. When ENA is high, the channel A is enabled. ENA is enabled by default due to the internal pull-up resistor. Recommend to connect the ENA to VDD if this pin is not used.         |

| 2   | INA  | Input of channel A. the OUTA is in phase with INA. OUTA is held low if INA is floating due to the internal pull down resistor. Recommend to connect the INA to ground if this pin is not used.                                                                                              |

| 3   | GND  | Ground. All signals are referenced to this pin.                                                                                                                                                                                                                                             |

| 4   | INB  | Input of channel B. the OUTB is in phase with INB. OUTB is held low if INB is floating due to the internal pull down resistor. Recommend to connect the INB to ground if this pin is not used.                                                                                              |

| 5   | OUTB | Output of channel B.                                                                                                                                                                                                                                                                        |

| 6   | VDD  | Bias Supply Input.                                                                                                                                                                                                                                                                          |

| 7   | OUTA | Output of channel A                                                                                                                                                                                                                                                                         |

| 8   | ENB  | Enable input for channel B. When ENB is low, the channel B output is disabled regardless of the INB state. When ENB is high, the channel B is enabled. ENB is enabled by default due to the internal pull-up resistor. It is recommended to connect the ENB to VDD if this pin is not used. |

|     | EP   | Exposed pad, connect to ground. Only for MSOP8-EP                                                                                                                                                                                                                                           |

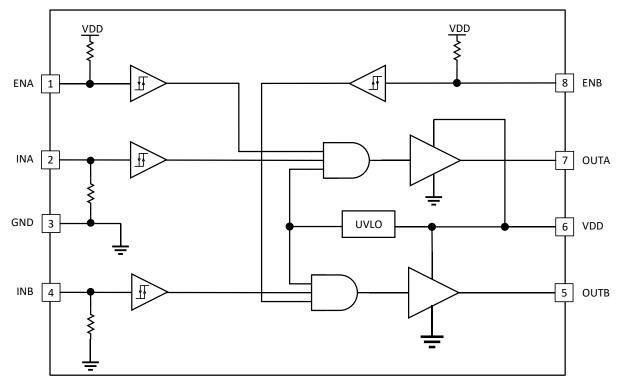

# FUNCTIONAL BLOCK DIAGRAM

Figure 2. SiLM27624 Block Diagram

## **ABSOLUTE MAXIMUM RATINGS<sup>1,2,3</sup>**

| Symbol             | Description                                   | Min. | Max.                 | Units |  |

|--------------------|-----------------------------------------------|------|----------------------|-------|--|

| V <sub>DD</sub>    | Supply voltage                                | -0.3 | 33                   |       |  |

| OUTA, OUTB         | Continuous voltage on OUTx                    | -0.3 | V <sub>DD</sub> +0.3 | V     |  |

| 001A, 001B         | Repetitive pulse less than 200ns <sup>4</sup> | -2   | V <sub>DD</sub> +0.3 |       |  |

| INA, INB, ENA, ENB | Voltage on INA, INB, ENA, ENB.                | -6   | 33                   | V     |  |

| TJ                 | Operation junction temperature range          | -40  | 150                  |       |  |

| T∟                 | Lead temperature (soldering, 10 seconds)      |      | 300                  | °C    |  |

| Ts                 | Storage temperature                           | -55  | 150                  |       |  |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2) All voltages are with respect to GND unless otherwise noted.

- 3) These devices are sensitive to electrostatic discharge; follow proper device-handling procedures.

- 4) Values are verified by characterization on bench.

## **RECOMMENDED OPERATION CONDITIONS**

Over operating free-air temperature range (unless otherwise noted)

| Symbol          | Definition                           | Min | Max | Units |

|-----------------|--------------------------------------|-----|-----|-------|

| V <sub>DD</sub> | Supply voltage                       | 4.5 | 30  |       |

| INA, INB        | Input voltage                        | -5  | 30  | V     |

| ENA, ENB        | Enable voltage                       | -5  | 30  |       |

| TJ              | Operation junction temperature range | -40 | 150 | °C    |

## **ORDERING INFORMATION**

| Order Part No.  | UVLO  | Package           | QTY       |

|-----------------|-------|-------------------|-----------|

| SiLM27624LCA-DG | 4.2V  | SOP8, Pb-Free     | 2500/Reel |

| SiLM27624LGB-DG | 4.2V  | MSOP8-EP, Pb-Free | 4000/Reel |

| SiLM27624MCA-DG | 8.5V  | SOP8, Pb-Free     | 2500/Reel |

| SiLM27624MGB-DG | 8.5V  | MSOP8-EP, Pb-Free | 4000/Reel |

| SiLM27624HCA-DG | 12.5V | SOP8, Pb-Free     | 2500/Reel |

| SiLM27624HGB-DG | 12.5V | MSOP8-EP, Pb-Free | 4000/Reel |

5

## DYNAMIC ELECTRICAL CHARACTERISTICS

$V_{DD}$  = 12V,  $T_A$ = $T_J$ = - 40°C to 125°C, typical values are specified at 25 °C unless otherwise noted.

| Symbol           | Parameter                                                            | Condition                                             | Min | Тур | Max | Unit |

|------------------|----------------------------------------------------------------------|-------------------------------------------------------|-----|-----|-----|------|

| t <sub>R</sub>   | Rise time <sup>1</sup>                                               | C <sub>LOAD</sub> = 1.8 nF                            |     | 7   | 11  |      |

| t⊧               | Fall time <sup>1</sup>                                               | C <sub>LOAD</sub> = 1.8 nF                            |     | 6   | 8.4 |      |

| t⋈               | Delay matching between two channels                                  | INA = INB, OUTA and OUTB at 50% transition point      |     |     | 2   |      |

| tpw              | Minimum input pulse width that changes the output state <sup>2</sup> |                                                       |     | 13  | 15  | ns   |

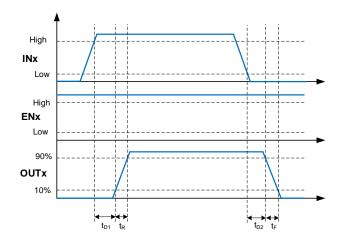

| $t_{D1}, t_{D2}$ | Input to output propagation delay <sup>1</sup>                       | $C_{LOAD} = 1.8 \text{ nF}, 5 \text{ V}$ input pulse  |     | 20  | 27  |      |

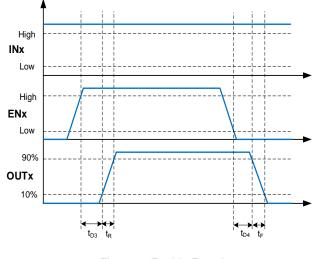

| td3, td4         | EN to output propagation delay <sup>1</sup>                          | $C_{LOAD} = 1.8 \text{ nF}, 5 \text{ V}$ enable pulse |     | 20  | 27  |      |

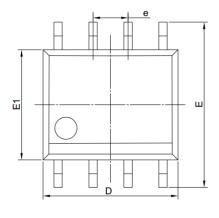

1) See timing diagrams in Figure 3 to Figure 4.

2) Values are verified by characterization on bench.

## STATIC ELECTRICAL CHARACTERISTICS

$V_{DD}$  = 12V,  $T_A$ =T<sub>J</sub>= - 40°C to 125°C, typical values are specified at 25 °C unless otherwise noted.

| Symbol                               | Parameter                  | Condition                                                     | Min  | Тур  | Мах  | Unit |

|--------------------------------------|----------------------------|---------------------------------------------------------------|------|------|------|------|

| Ivdd_off                             | VDD startup current        | V <sub>DD</sub> = 3.4 V, ENA = ENB =<br>VDD, INA=INB=3.3V     |      | 110  | 270  | μA   |

| Ivdd                                 | VDD static current         | ENA=ENB=VDD,<br>INA=INB=3.3V                                  |      | 810  | 1300 | μA   |

|                                      |                            | ENA=ENB=VDD,<br>INA=INB=0V                                    |      | 600  | 900  | μA   |

| Ivdd_op                              | VDD operating current      | ENA=ENB=VDD,<br>INA = INB =PWM, 1000kHz, no<br>load at output |      | 3.6  | 4.1  | mA   |

| Ivdd_dis                             | VDD disable current        | INA=INB = 3.3 V,<br>ENA = ENB = GND                           |      | 630  | 900  | μA   |

| Under Volta                          | age Lockout (UVLO)         |                                                               |      |      |      |      |

|                                      |                            | SiLM27624L                                                    | 3.9  | 4.2  | 4.5  | V    |

| $V_{\text{DD}\_\text{UV}\_\text{R}}$ | VDD UVLO rising threshold  | SiLM27624M                                                    | 8    | 8.5  | 9    | V    |

|                                      |                            | SiLM27624H                                                    | 11.5 | 12.5 | 13.5 | V    |

|                                      |                            | SiLM27624L                                                    | 3.6  | 3.9  | 4.2  | V    |

| $V_{\text{DD}\_\text{UV}\_\text{F}}$ | VDD UVLO falling threshold | SiLM27624M                                                    | 7    | 7.5  | 8    | V    |

|                                      |                            | SiLM27624H                                                    | 10.5 | 11.5 | 12.5 | V    |

| VDD_UV_HYS                           | VDD UVLO hysteresis        | SiLM27624L                                                    |      | 0.3  |      | V    |

| ע_טע_нזצ                             |                            | SiLM27624M                                                    |      | 1.0  |      | V    |

Sillumin Semiconductor Co., Ltd. - www.sillumin.com

# SILUMIN

| Symbol              | Parameter                        | Condition                | Min  | Тур  | Max  | Unit     |

|---------------------|----------------------------------|--------------------------|------|------|------|----------|

|                     |                                  | SiLM27624H               |      | 1.0  |      | V        |

| Input (INA          | , INB)                           |                          |      |      |      |          |

| V <sub>IN_H</sub>   | Input signal high threshold      |                          | 1.8  | 2    | 2.3  | V        |

| V <sub>IN_L</sub>   | Input signal low threshold       |                          | 0.8  | 1    | 1.2  | V        |

| V <sub>IN_HYS</sub> | Input signal hysteresis          |                          |      | 1    |      | V        |

| R <sub>IN</sub>     | Inx pin pulldown resistor        | INx=3.3V                 |      | 120  |      | kΩ       |

| Enable (El          | NA, ENB)                         | I                        |      |      |      | <u> </u> |

| Ven_h               | Enable signal high threshold     |                          | 1.8  | 2    | 2.3  | V        |

| Ven_L               | Enable signal low threshold      |                          | 0.8  | 1    | 1.2  | V        |

| Ven_hys             | Enable signal hysteresis         |                          |      | 1    |      | V        |

| Ren                 | Enx pin pullup resistor          | ENx=0V                   |      | 200  |      | kΩ       |

| Output (O           | UTA, OUTB)                       |                          | I    |      |      |          |

| ISRC                | Source peak current <sup>1</sup> | C <sub>L</sub> = 0.22 μF |      | 5.0  |      | A        |

| I <sub>SNK</sub>    | Sink peak current <sup>1</sup>   | C <sub>L</sub> = 0.22 μF |      | 5.0  |      | A        |

| Vон                 | High level output voltage        | Io = -10 mA, VDD-Vo      |      | 7.2  | 14   | mV       |

| V <sub>OL</sub>     | Low output voltage               | I <sub>O</sub> = 10 mA   |      | 4.5  | 8.5  | mV       |

| Rон                 | Output pull-up resistance        | I <sub>0</sub> = -10 mA  | 0.52 | 0.72 | 1.2  | Ω        |

| Rol                 | Output pull-down resistance      | lo = 10 mA               | 0.26 | 0.45 | 0.74 | Ω        |

1) Values are verified by characterization on bench.

Figure 3. Enable Function

Sillumin Semiconductor Co., Ltd. – <u>www.sillumin.com</u>

Feature Description

#### VDD and Under-Voltage Lockout

The SiLM27624 device has internal UVLO protection feature on the VDD pin supply. Whenever the driver is in UVLO condition (for example when  $V_{DD}$  voltage is less than  $V_{DD\_UV\_R}$  during power up and when VDD voltage is less than  $V_{DD\_UV\_R}$  during power up and when VDD voltage is less than  $V_{DD\_UV\_F}$  during power down), this circuit holds all outputs low, regardless of the status of the inputs. This hysteresis helps prevent chatter when low  $V_{DD}$  supply voltage have noise from the power supply and also when there are droops in the VDD bias voltage when the system starts switching and there is a sudden increase in  $I_{DD}$ .

#### Input Stage

The input pins of the SiLM27624 gate-driver are based on a TTL and CMOS compatible input threshold logic that is independent of the VDD supply voltage. With typically high threshold = 2 V and typically low threshold = 1 V, the logic level thresholds are conveniently driven with PWM control signals derived from 3.3V and 5V digital power-controller devices. SiLM27624 also features tight control of the input pin threshold voltage levels which eases system design considerations and ensures stable operation across temperature.

The SiLM27624 features an important safety feature wherein, whenever any of the input pins is in a floating condition, the output of the respective channel is held in the low state. This is achieved using pull-down resistors on the INA and input pins.

The input stage of each driver is driven by a signal with a short rise or fall time. This condition is satisfied in typical power supply applications, where the input signals are provided by a PWM controller or logic gates with fast transition times (<200 ns) with a slow changing input voltage, the output of the driver may switch repeatedly at a high frequency. While the wide hysteresis offered in SiLM27624 definitely alleviates this concern over most other TTL input threshold devices, extra care is necessary in these implementations. If limiting the rise or fall times to the power device is the primary goal, then an external resistance is highly recommended between the output of the driver and the power device.

#### **Enable Function**

SiLM27624 is provided with independent enable pins ENx for exclusive control of each driver-channel operation. The enable pins are based on a non-inverting configuration (active high operation). Thus, when ENx pins are driven high, the drivers are enabled and when ENx pins are driven low, the drivers are disabled. Like the input pins, the enable pins are also based on a TTL and CMOS compatible input threshold logic that is independent of the supply voltage and are effectively controlled using logic signals from 3.3V and 5V microcontrollers. The SiLM27624 also features tight control of the enable function threshold voltage levels which eases system design considerations and ensures stable operation across temperature. The ENx pins are internally pulled up to VDD using pull-up resistors as a result of which the outputs of the device are enabled in the default state. Hence the ENx pins are left floating or Not Connected (N/C) for standard operation, where the enable feature is not needed. If the channel A and channel B inputs and outputs are connected in parallel to increase the driver current capacity, ENA and ENB are connected and driven together.

The enable function is an extremely beneficial feature in gate driver devices especially for certain applications such as synchronous rectification where the driver outputs disabled in light load conditions to prevent negative current circulation and to improve light load efficiency.

#### **Output Stage**

Each output stage in the SiLM27624 device is capable of supplying 5.0 A peak source and 5.0 A peak sink current pulses. The output voltage swings between VDD and GND providing rail-to-rail operation, thanks to the MOS-output stage which delivers very low drop-out.

The channel A and channel B outputs can be paralleled to provide higher driver current capability. In such application, the INA and INB need to be connected together and ENA, ENB also need be connected together.

For example, in applications that have zero voltage switching during power MOSFET turn-on or turn-off interval, the driver supplies high-peak current for fast switching even though the miller plateau is not present. This situation often occurs in synchronous rectifier applications because the body diode is generally conducting before power MOSFET is switched on.

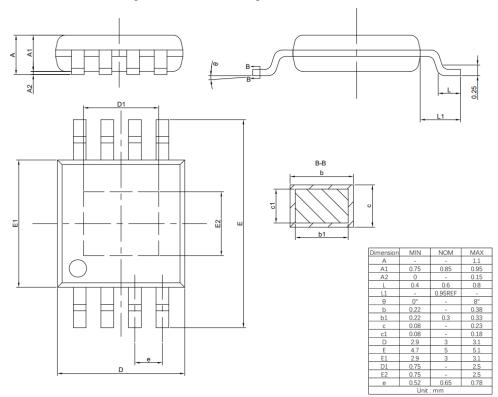

## **PACKAGE CASE OUTLINES**

| Dimension | MIN  | NOM   | MAX  |

|-----------|------|-------|------|

| Α         | -    | -     | 1.75 |

| A1        | 0.1  | -     | 0.25 |

| A2        | 1.25 | -     | -    |

| L         | 0.4  | 0.835 | 1.27 |

| L1        | -    | 1.04  | -    |

| θ         | 0    | -     | 8    |

| b         | 0.31 | -     | 0.51 |

| b1        | 0.28 | -     | 0.48 |

| С         | 0.1  | -     | 0.25 |

| c1        | 0.1  | -     | 0.25 |

| D         | 4.7  | 4.9   | 5.1  |

| E         | 5.8  | 6     | 6.2  |

| E1        | 3.8  | 3.9   | 4    |

| е         | 1.02 | 1.27  | 1.52 |

| Unit : mm |      |       |      |

#### Figure 5. SOP8 Package Outline Dimensions

Figure 6. MSOP8-EP Package Outline Dimensions

## **REVISION HISTORY**

Note: page numbers for previous revisions may differ from page numbers in current version

| Page or Item                 | Subjects (major changes since previous revision)                  |  |  |

|------------------------------|-------------------------------------------------------------------|--|--|

| Rev 1.0 Datasheet 6/May/2023 |                                                                   |  |  |

| Whole document               | Initial released                                                  |  |  |

| Rev 1.1 Datasheet Sep/2023   |                                                                   |  |  |

| Page 6                       | Revise I <sub>VDD</sub> , I <sub>VDD_DIS</sub> Unit from mA to µA |  |  |